### **IPSR-I ENABLING TECHNOLOGIES**

## **TEST TWG**

#### Contents

| Executive summary                                  | 1  |

|----------------------------------------------------|----|

| Introduction                                       |    |

| Roadmap of Quantified Key Attribute Needs          | 6  |

| On-Wafer Testing                                   | 6  |

| Bar / die testing                                  | 9  |

| Life cycle testing (Mounted dies but also earlier) | 10 |

| Testing parameters of production processes         | 11 |

| Situation analyses                                 | 19 |

| Manufacturing processes                            |    |

| Design                                             | 19 |

| Wafer level Testing                                | 21 |

| Bare die level Testing                             | 22 |

| Generic Photonic Device Testing                    | 22 |

| General Test Equipment                             |    |

| Critical (infrastructure) issues                   |    |

| Technology needs (related to Milestones)           |    |

| Prioritized Research Needs                         |    |

| Prioritized Development & Implementation Needs     |    |

| Design                                             |    |

| Standardization of test metrics and qualification  | 29 |

| Tools and methods                                  |    |

| High throughput testing (sub second per chip)      | 31 |

| Workforce development                              |    |

| Gaps and showstoppers                              |    |

| Standarization                                     |    |

| Platform agnostic testing                          |    |

| Automation                                         |    |

| High speed (rf bandwidth) testing                  |    |

| Optical testing for manufacture                    |    |

| User support                                       |    |

|                                                    |    |

### **IPSR-I** ENABLING TECHNOLOGIES

| Analysis of testing results                           |  |

|-------------------------------------------------------|--|

| Cost                                                  |  |

| Higher PIC technologies                               |  |

| Recommendations on Potential Alternative Technologies |  |

| Contributors                                          |  |

#### **EXECUTIVE SUMMARY**

In the electronic integrated circuit (EIC) industry, testing has become a mature process supported by practices and equipment that have been heavily optimized to drive down the cost and time spent on IC testing. In contrast, development of similar methods and tools for the photonic integrated circuit (PIC) community is still at an early stage and the extra complexity that arises from having to measure both in the optical and the electrical domain poses many challenges. In this chapter we define a number of key areas where development is needed and in each of these areas we strive to leverage as much as possible the existing knowledge, practices and infrastructure from the EIC industry.

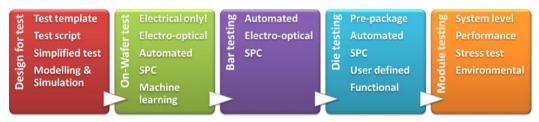

Figure 1. Overview of the test processes across the manufacturing chain of photonic integrated circuit based modules. Statistical process controls (SPC) require adequate test methods and data collection plans which should be accounted for already at the design phase.

The term PIC refers to an immensely diverse field of different implementations where we need to consider different (1) materials (InP, GaAs, Si, polymer, Triplex, glass), (2) integration schemes (monolithic, hybrid, etc.), (3) packaging (hermetic, non-hermetic, material) and (4) optical couplers (gratings, edge, mirrors coupled to single fibers, fiber arrays, lensed fibers, etc.). This leads to a first key development area: standardization of test metrics. New standardized testing methodologies and qualification parameters need to be devised that apply to all technologies, types of packages, and all relevant environmental conditions – leading to a truly platform-agnostic test solution.

A second focus area is to consolidate the design and test workflow (see example in Figure 1). A four-step method is proposed to enhance collaboration between designers, fab engineers and test engineers. Variations in dimensional and physical properties of materials and modules need to be understood and taken into account during design. This permits engineers to predict the influence of process variations on measurement results and allows them to design dedicated and improved test structures up front. By repeating these steps in combination with a careful analysis of the stored data, the number of devices to be measured and tracked can be reduced and the functional yield is expected to increase.

This targeted reduction in number of devices brings us to a third key area: test time reduction. There is a clear need for fully automated test systems. On the one hand this includes inline and where possible in-situ process testing at wafer level such as critical-dimension (CD) monitoring, defects counting, ellipsometry, etc. On the other hand, this includes the (out-of-line) automatic functional testing at wafer, bar/die and module level. For the functional test a massively parallel test approach is envisaged in order to bring down measurement time and cost.

More specifically for wafer-level testing, this highly parallel test approach can be enabled by scalable and modular test equipment and an increase in the number of electrical and optical input-output (IO) ports per test site. For electrical measurement instrumentation this modular approach is already quite well established; for optical instruments this is an emerging concept. In order to increase the number of optical IOs per test site from 10s to 100s of couplers in the next 10 years, multi-core fibers or fiber arrays will have to be used in combination with an optical interposer to reduce the pitch of optical IOs. Measuring optical signals indirectly using on-chip photodiodes is another interesting option to eliminate the need for optical alignment.

In contrast to silicon photonic (SiPh) chips, InP- and GaAs-chips often require bar /die level testing. Main reason is that often cleaved facets with ultra-low antireflection coating is needed for full device operation. In the future the target will be to replace cleaved facets by on-wafer etched facets and to replace facet coating by on-wafer coating. Then most of the bar / die testing can be avoided and wafer level testing can be used. In case of SiN devices it is expected that also in future die testing will play an important role.

In addition to functional testing, also the area of reliability / lifetime testing needs to be addressed. To date commercially available life time testing equipment is mainly based on fiber attached mounted single dies or mounted single devices that are being tested with free space measurement setups (e.g. laser lifetime measurements using large area photodiodes). Such investigations therefore cause high costs. Performing these tests at wafer level, simultaneously on multiple dies is an option to be investigated. This will also require developments in terms instrumentation, e.g. high-power laser sources for accelerated lifetime testing.

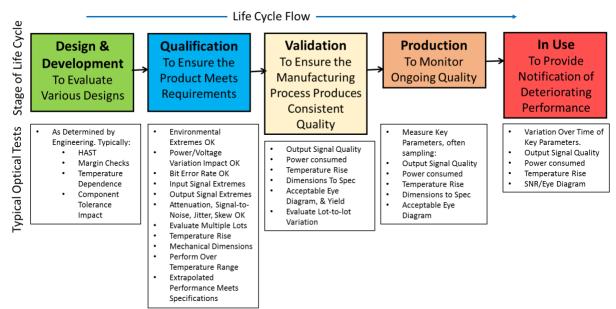

The IPSR-I Test TWG addresses overall lifetime test issues resulting from the inclusion of photonic capabilities into devices and products. Its emphasis is on wafers and dies with photonic functionality and assemblies and products that include these devices. Systems in Package (SiP), assemblies and bulk systems are addressed to the extent viable given the diversity of test needs that are specific to applications. As shown in Figure 2, the test issues for wafers, die, SiP, and systems will be addressed at the Design, Qualification, Validation, Production, and In-Use stages of product life cycles<sup>1</sup>. Current and anticipated optical parameters to be tested and their value or level are considered along with the test access issue at each stage of the product life cycle.

Figure 2 Test Needs During an Optical Product Life Cycle

<sup>&</sup>lt;sup>1</sup> Testing and evaluation during Photonic Integrated Circuit (PIC) fabrication is specifically excluded and left for the Monolithic Photonic Integration chapter.

Telecommunications test equipment, components, and methods were and are being adopted for optical testing of products used for non-long haul applications. The traditional methods are being extended and new methods developed to address test needs for photonic wafers, photonic integrated circuits, and SiP that utilize optics and complete systems. Utilizing these extended methods requires optical probing of both wafers and dies combined with electrical probing resulting in a series of mechanical issues. The inclusion of optical probing, especially single mode probing, requires gratings or other access points on wafers. For individual die, dual mode (electrical and optical) probing is especially difficult due to the small size of die and difficulty of holding and locating probes accurately. At the SiP level, the problems are easier because the device is larger, not as fragile, and is often designed to facilitate dual media probing. The wafer, die, and SiP probe fixtures tend to be expensive due to the complexity and accuracy required. System level test access is usually easier because at that level, electrical interfaces and optical connectors are included as part of the device under test (DUT).

In addition to probe access, optical test methods to simultaneously characterize and compare multiple optical lanes, channels and/or ports at the same time are needed. One need is comparative simultaneous testing of multiple signals from arrays of ribbon fibers, waveguides, sources or detectors for optical skew, jitter, etc. A related need is to simultaneously evaluate optical signals multiplexed on one fiber or waveguide. Applications with arrays exceeding 256 ports (fibers or waveguides) or >256 multiplexed wavelengths are forecast in the next ten years.

In addition to the standard telecom optical parameters such as power, wavelength, attenuation, jitter, signal-to-noise ration (SNR), etc., emerging applications aim to utilize virtually every parameter that light can have, potentially requiring the extension of test capability in multiple dimensions such as polarization, phase noise, amplitude noise spatial modes, multiple fiber cores, etc. While these emerging needs are potentially very broad, the near-term emerging needs seem most likely to be extensions of data communications needs.

Optical communication applications are likely to utilize 650 nm to 2000 nm wavelengths, multiplexed wavelength spacing down of 25 GHz, detector responsivity of ~1 A/W, receiver sensitivity as great as -45 dBm, power levels of 1 Watt or less, symbol rates of 100 Gbaud per lane, modulation schemes utilizing up to 10 bits per symbol, polarization multiplexing, BERs of  $10^{-12}$ , etc. Over time, these parameters will improve so test capabilities will need to stay ahead of them. Data rates as high as 500 Tbps per fiber are likely to emerge in the next 10- 15 years.

Sensor applications are likely to grow significantly in the next 10-15 years as remote fiber sensors are integrated into physical structures for strain and temperature sensing, and as chip-level chemical and biological sensors are introduced into the marketplace. While these applications will still require the same baseline test solutions as is required for telecom and datacom, the functional tests are likely to be quite different.

Quantum technologies add yet a different dimension for testing. The use of single photon and entangled-photon sources and circuits will yield its own complexity. There is currently no standardized test equipment for these applications; however, testing methods are currently being developed with University, Government, and Industrial research labs and will require consideration in future editions of this document.

# **REGARDLESS OF APPLICATION, THE PRINCIPLES OF** *DESIGN FOR TEST* **REMAIN THE SAME: THE USE OF** OPTICAL TEST ACCESS POINTS, BUILT-IN SELF-TEST (BIST), REDUNDANCY FOR SELF-REPAIR, RE-PURPOSE AND PROGNOSTICS TO REPORT CHANGES AND DETERIORATION DURING OPERATION OVER THE LIFE CYCLE OF OPTICAL PRODUCTS ARE DESIRABLE AND OF VALUE IN AN INCREASING NUMBER OF APPLICATIONS. THESE TESTS SHOULD BE CONSIDERED FOR INCLUSION NOT ONLY IN DESIGNS, BUT ALSO IN SOFTWARE DESIGN TOOLS AS WELL.INTRODUCTION

The Test chapter focuses on unique attributes of testing optical devices. No attempt has been made to duplicate required and typical electrical or mechanical testing. The chapter is open ended on optical applications testing with much of the material broadly applicable. It does, however, concentrate primarily on testing data communications products.

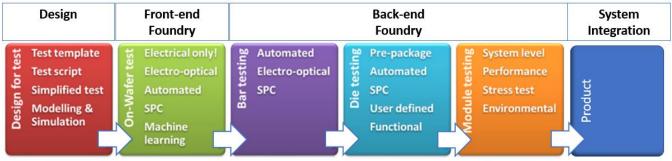

Figure 3 An overview of the PIC production chain for test.

In each step of the test chain that is followed by the components that will form an end product different requirements and methods are used. This chapter will discuss both the separate steps, as the connection between those steps regarding the product and data flow.

Areas of testing need during a product life cycle are:

- a. during development to prove functionality and de-bug devices

- b. qualification testing

- c. pre-production validation

- d. in-process production testing to assure product quality, reliability and to improve yield.

This chapter contains an overview of PICs made on InP, SiN, SiPh, GaAs, Polymers and CMOS platforms. Elements like fiber couplers, fiber arrays, lenses, optical and electrical interconnects and the standardization of test port positions (optical, DC, RF) will also be discussed.

The kinds of testing required vary over the life cycle of a product (Figure 2). Test Needs during an Optical Product Life Cycle lists typical optical device test activities and requirements during the life of a device from conception through the in-use and end of life phases.

#### Lanes vs Channels

An optical lane utilizes one wavelength traveling from one point to another in one fiber or waveguide. Information may be imposed on the beam utilizing any methods such as On-Off-Keying, PAM XX, dual polarization or any method that effects only that wavelength.

A Channel may consist of a single lane but often, even usually, has multiple lanes. The lanes may be on multiple parallel fibers or waveguides, or on the same fiber or waveguide utilizing wavelength division multiplexing. Many datacom standards utilize multiple lanes to achieve their data rates.

Evaluating technical capability is most easily done utilizing lanes because channels that combine many lanes make it difficult to understand the underlying technology. System designers, however, find the channel view more useful as the technology details are not important at their level.

## Prescriptive Starts Here

#### **ON-WAFER TESTING**

Ideally, the estimation of the yield of a wafer for a particular PIC product occurs on-wafer at the final stage of the fabrication. This way, the number of handling steps can be reduced, and even eliminated (such as the handling of the bars during the bar-level tests). On-wafer electrical- and optical testing is possible for PIC products by introducing the grating couplers and/or vertical mirrors into the PIC fabrication process. As a result, the grating couplers and/or vertical mirrors on the wafer need to be coated on wafer level, and the electrical measurements have to be done in a pulsed-mode operation (preferably with standardized pulse widths). Therefore, for those PIC products that do not require endface coupling, this solution is ideal in that all the relevant testing from PIC performance, to far-field measurements of the grating couplers/vertical mirrors can be done in a straightforward manner.

Most optical measurements of devices such as measurement of optical waveguide losses require the use of vertical in/out grating couplers or angled mirrors. Furthermore on-wafer facet coating of all devices will be needed to significantly reduce all bar and die measurements. For the electrical wafer testing mature electrical tools will be used. The amount of I/O will increase in future. Today typically 4 and 16 I/O are used:

|                      | [unit]      | 2020            | 2025                       | 2030                                          | 2035               | 2040               |

|----------------------|-------------|-----------------|----------------------------|-----------------------------------------------|--------------------|--------------------|

| # of Optical I/O     | per<br>chip | 16              | 32                         | 64                                            | 128                | 256                |

| Pitch of Optical I/O | μm          | 256             | 127                        | 65                                            | 20                 | 15                 |

| Optical I/O Geometry |             | Linear<br>Array | Stacked<br>Linear<br>Array | Small<br>diameter<br>or<br>multicore<br>fiber | Multicore<br>fiber | Multicore<br>fiber |

Table 1 On-wafer testing

By use of fibre arrays, multicore fibres or different multiple I/O optical probe technology a parallelization of the measurements will be achieved in future. To this end, standardized input/output gratings couplers will be used to match the chosen optical probe technology. On the other hand, such measurements will be possible only if suitable modular and scalable measurement equipment is available, e.g. multi-channel and fast high power tunable laser sources, multi-port power meters, polarization controls, optical switch matrixes,

The following tables summarize the current status and the expected development of the device testing within the next 15 years. Laser diodes (LD), photo-detectors (PD) and Mach–Zehnder Modulators (MZM) are considered for different fabrication technologies as applicable: and Table 2 for silicon, Table 3 for InP and GaAs and Table 4 for SiN.

Table 1 Wafer level high throughput testing -Si-Photonics

| Wafer level high<br>throughput testing -<br>Silicon-Photonics                                                                                 | [unit]                            | 2020                                | 2025                                    | 2030                                          | 2035                                                    | 2040                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------|-----------------------------------------|-----------------------------------------------|---------------------------------------------------------|------------------------|

| Propagation loss<br>ex. Si-wire, polymer, and<br>rib waveguides<br>(measure some<br>waveguides per chip)                                      | [dB/cm<br>]                       |                                     |                                         | 5-10<br>min/chip                              |                                                         |                        |

| Insertion loss<br>ex. modulators (measure<br>some devices per chip)                                                                           | [dB]                              | 30<br>min/chip<br>Semi-             | 5-20<br>min/chip*<br>Fully<br>automated | with<br>2-4 probes<br>(1-5 min/2-<br>4 chips) | 2-5 min/chip<br>multi 4-8 pro<br>(0.5-2 min/4-          |                        |

| Spectrum (Operating<br>wavelength)<br>ex. Grating couplers,<br>Directional couplers, Ring<br>resonators<br>(measure some devices per<br>chip) | [dBm/<br>nm]                      | automated                           |                                         |                                               | (0.5-2 1111/4-                                          | o cmps <i>)</i>        |

| Contact resistance                                                                                                                            | $\left[ \Omega \atop cm^2  ight]$ | use current/mature electrical tools |                                         |                                               |                                                         |                        |

| Sheet resistance                                                                                                                              | $[\Omega/sq]$                     |                                     | ſ                                       | ſ                                             | ſ                                                       |                        |

|                                                                                                                                               | [V cm<br>(or V)]                  |                                     |                                         |                                               |                                                         |                        |

| f <sub>3dB</sub> (EO bandwidth)<br>ex. MZI/Ring modulators                                                                                    | [GHz]                             |                                     |                                         | 5 min per<br>device or<br>circuit<br>fully    | 2 min per<br>device or<br>circuit<br>fully<br>automated |                        |

| Responsivity<br>ex. Ge photodiode                                                                                                             | [A/W]                             | 20 min per<br>device or             | 10 min per<br>device or                 |                                               |                                                         | 1 min per<br>device or |

| Dark Current<br>ex. Ge photodiode                                                                                                             | [nA]                              | circuit<br>semi-                    | circuit<br>semi-                        |                                               |                                                         | circuit<br>fully       |

| f <sub>3dB</sub> (EO bandwidth)<br>ex. Ge photodiode                                                                                          | [GHz]                             | automated                           | automated                               | automated                                     |                                                         | automated              |

| Eye pattern<br>ex. MZI/Ring modulators,<br>Ge photodiode                                                                                      |                                   |                                     |                                         |                                               |                                                         |                        |

| BER (Bit Error Rate)<br>ex. MZI/Ring modulators,<br>Ge photodiode                                                                             |                                   |                                     |                                         |                                               |                                                         |                        |

| environmental testing<br>ex. temperature -40 to<br>+85 °C.                                                                                    |                                   | Adapt curren                        | t/mature enviro                         | onmental tools                                |                                                         |                        |

\* not including wafer load/unload time (Front Opening Universal Pod (FOUP/Front Opening Shipping Box (FOSB) to testing state to FOUP/FOSB).

| Parameter                       | Unit                  | Test Level  | Test Time Goal |

|---------------------------------|-----------------------|-------------|----------------|

| output power – laser diode (LD) | [mW]                  | bar level   |                |

| threshold current LD            | [mW]                  | bar level   |                |

| SMSR LD                         | [dB]                  | bar level   |                |

| RIN LD                          | [dBc/Hz]              | bar level   | 1 min/device   |

| Frequency noise spectrum LD     | [Hz <sup>2</sup> /Hz] | die level   |                |

| Frequency response LD           | [GHz]                 | die level   |                |

| Extinction Ratio LD             | [dB]                  | die level   |                |

| Sensitivity MZM                 | $[V_{2\pi}]$          | bar level   |                |

| Modulation bandwidth MZM        | [GHz]                 | bar level   | 2 min/device   |

| Insertion loss MZM              | [dB]                  | bar level   |                |

| Responsivity PD                 | [A/W]                 | wafer level | 1 min/device   |

| Bandwidth PD                    | [GHz]                 | wafer level |                |

Table 3 High throughput testing of InP and GaAs devices

Table 4 Wafer level Inspection- SiN devices

| Parameter              | Unit            | Test Level  | Inspection Time Goal |

|------------------------|-----------------|-------------|----------------------|

| Layer stack quality    | Particle        | Experienced | 5 min                |

| Layer stack quanty     | density         | eye         | 5 mm                 |

| Lithography quality    | Resolution test | manual      | 5 min                |

|                        | & defect count  |             |                      |

| Etching quality        | Compare with    | Microscope  | 5 min                |

|                        | litho check     | manual      |                      |

| Top cladding quality   | Visual defect   | Microscope  | 10 min               |

|                        | check           | manual      |                      |

| Actuator check         | Visual defect   | Microscope  | 5 min                |

|                        | check           | manual      |                      |

| Wafer level bump check | Visual defect   | Microscope  | 10 min               |

|                        | check           | manual      |                      |

BAR / DIE TESTING

In contrast to Si-photonic the InP- and GaAs-chips often require on bar /die testing (see table below).

Main reason is that often cleaved facets with ultra-low antireflection coating is needed for full device operation. In the future the target is to replace cleaved facets by on-wafer etched facets and to replace facet coating by on-wafer coating. Then most of the bar / die testing can be avoided and wafer level testing can be used.

In case of SiN devices it is expected that also in future die testing will play an important role.

|                                | [unit]                | 2020   | 2025     | 2030                      | 2035          | 2040 |

|--------------------------------|-----------------------|--------|----------|---------------------------|---------------|------|

| output power LD                | [mW]                  | serial | parallel | parallel waf              | er level test |      |

| threshold current LD           | [mW]                  | serial | parallel | parallel waf              | er level test |      |

| SMSR LD                        | [dB]                  | serial | parallel | parallel waf              | er level test |      |

| RIN LD                         | [dBc/Hz]              | serial | parallel | parallel waf              | er level test |      |

| Frequency noise<br>spectrum LD | [Hz <sup>2</sup> /Hz] | serial | parallel | parallel wafer level test |               |      |

| Frequency response LD          | [GHz]                 | serial | parallel | parallel wafer level test |               |      |

| Extinction Ratio LD            | [dB]                  | serial | parallel | parallel wafer level test |               |      |

| Sensitivity MZM                | [V <sub>2π</sub> ]    | serial | parallel | parallel wafer level test |               |      |

| Modulation bandwidth<br>MZM    | [GHz]                 | serial | parallel | parallel wafer level test |               |      |

| Insertion loss MZM             | [dB]                  | serial | parallel | parallel waf              | er level test |      |

#### Table 3 Die testing SiNx-devices

| Die testing<br>SiNx-<br>devices | [unit]                                                 | 2020                                                                                                                                    | 2025                                                                                                     | 2030                               | 2035          | 2040         |

|---------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------|---------------|--------------|

| Waveguide<br>defect check       | #<br>defects/chi<br>p<br>% of defect<br>chips<br>yield | End facet<br>incoupling of<br>light and VIS<br>& IR monitor<br>on top of chip-<br>Manual place,<br>Auto align.<br>Operator<br>required. | Auto place &<br>align and auto<br>record.<br>No operator.<br>Manual<br>analyze.<br>Obtain<br>statistics. | Full auto<br>analysis              | mation of acq | uisition and |

| Waveguide<br>loss check         | dB/ cm,<br>loss<br>spectrum                            | Manual place<br>& Auto<br>alignment to<br>loss test<br>structures.                                                                      | Auto place &<br>align & auto<br>measurement.<br>No operator.<br>Manual<br>analyze.                       | Auto plac<br>Auto alig<br>Auto ana | gn & measure  |              |

|                                                 |                                                          | Operator required.                                                           | Obtain statistics.                                                                                         |                                                     |

|-------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Building<br>block test<br>(DC, MMI,<br>RR, MZI) | Insertion<br>loss,<br>splitting<br>ratio, FSR,           | Manual place<br>& Auto<br>alignment and<br>measure.<br>Operator<br>required. | Auto place,<br>align & auto<br>measurement.<br>No operator.<br>Manual<br>analyze.<br>Obtain<br>statistics. | Auto place<br>Auto align & measure<br>Auto analysis |

| Actuators                                       | # Defects /<br>chip<br>Sensitivity<br>(V <sub>2π</sub> ) | Manual place<br>& Auto<br>alignment and<br>measure<br>Operator<br>required   | Auto place,<br>align & auto<br>measurement<br>No operator.<br>Manual<br>analyze.<br>Obtain<br>statistics.  | Full automation of acquisition and analysis         |

#### Life cycle testing (Mounted dies but also earlier)

To date commercially available life time testing equipment is mainly based on fibre attached mounted single dies or mounted single devices that are being tested with free space measurement setups (e.g. laser lifetime measurements using large area photodiodes). Such investigations therefore cause high costs. For some of the test conditions (e.g. high temperature, high humidity) it is not clear how the materials (e.g. epoxies) used for fiber attachment will behave, so we actually need to study (1) the reliability of the fiber attachment and (2) reliability of the opto-electrical components and make sure one reliability aspect does not affect results for the other.

In future a parallelization of these lifetime measurement will be tackled, operating a large number of devices on wafer scale at the same time avoiding the mounting of single dies. As to the testing of e.g. photodiodes or waveguides high power laser sources are needed (especially considering parallel testing and thus splitting the laser output over multiple channels). However, for lifetime testing of the devices including the mounting / bonding process, testing on die level will be required.

| Life cycle testing InP<br>and GaAs devices | [unit] | 2020        | 2025    | 2030        | 2035 | 2040 |

|--------------------------------------------|--------|-------------|---------|-------------|------|------|

| Optical output power                       | [mW]   | established |         |             |      |      |

| Threshold current                          | [mA]   | established |         |             |      |      |

| Optical wavelength                         | [nm]   | none        | started | established |      |      |

| SMSR                                       | [dB]   | none        | started | established |      |      |

| Responsivity                               | [A/W]  | none        | started | established |      |      |

#### Testing parameters of production processes

To guarantee stable and high yield production processes it is a stringent requirement to test a large variety of different processing parameters while processing the wafers. These parameters to be checked still strongly depend on the devices fabricated. However, with view to a steadily increasing monolithic integration depth the parameters to be checked per wafer will converge in future.

The most important processing parameters to be checked during the processing are:

- etch depth uniformity: nm resolution, over 1 micrometer etch depth

- waveguide sidewall roughness: sub nm resolution, over 1 micrometer depth

- layer thickness and refractive index: 1\*10-4 accuracy, versus speed of measurement

- waveguide width measurements: nm resolution

- resistance measurements of heaters

- conformal filling measurement

- photoluminescence: micrometer resolution

- particle analysis

- imbalance in coupler structures (trimming possible)

- atomic force microscope to determine grating depths (trimming possible)

- resist thickness and structure width

- doping levels

Furthermore, several components can be measured during the wafer processing before finalizing it. This characterization can be done by electrical/optical probing:

- photodiodes

- lasers

- heaters

- separation / isolation resistance

Table 8 Testing production processes polymer devices

|                                                                                                        | [unit]       | 2020                                 | 2025             | 2030                           | 2035                 | 2040        |  |

|--------------------------------------------------------------------------------------------------------|--------------|--------------------------------------|------------------|--------------------------------|----------------------|-------------|--|

| Dimensions (line width, hole diameter)                                                                 | [nm]         |                                      |                  |                                |                      |             |  |

| LER (Line Edge<br>Roughness) *1                                                                        | [nm]         | 1 nm (use mature CD SEM tool)        |                  |                                |                      |             |  |

| Film thickness                                                                                         | [nm]         |                                      |                  |                                |                      |             |  |

| Alignment precision<br>of lithography<br>(especially, pn ion<br>implantation for<br>optical modulator) | [nm]         | Use mature optical overlay equipment |                  |                                |                      |             |  |

| Passiveopticalproperties *2Propagation loss                                                            | [dB/c<br>m]  |                                      | 5-20<br>min/chip | 5-10<br>min/chip<br>(parallel) | 2-5 min/ch           | •           |  |

| Insertion loss                                                                                         | [dB]         |                                      | Fully            | 2-4 probes<br>(1-5 min         | (parallel) 4-8 probe | -           |  |

| Spectrum                                                                                               | [dBm<br>/nm] |                                      | automated        | w/2-4<br>chips)                | (0.5-2 min           | /4-8 chips) |  |

| Qualification of polymer materials                                                                     | °C           | Manual                               | Manual           | Automated                      |                      |             |  |

| Active and passive<br>polymer curing,<br>poling, Teng-Mann<br>testing control                          |              | Manual                               | Manual           | Automated                      |                      |             |  |

| Poling measurements                                                                                    |              | Manual                               | Manual           | Automated                      |                      |             |  |

| Electrical probe and<br>contact to polymer<br>materials                                                |              | Manual                               | Manual           | Automated                      |                      |             |  |

| EOpolymerr33performance(EOactivity in material)                                                        | pm/V         | Established                          | Mature           | Mature                         |                      |             |  |

\*1 LER: Si top LER can be measured, but side wall roughness cannot be measured directly.

Correlation between CD SEM and optical properties should be investigated using image analysis and empirical approach.

\*2 Contactless and non-destructive inline optical testing (with no particle pollution)

|                                                               | [unit] | 2020                  | 2025                        | 2030                  | 2035        | 2040            |

|---------------------------------------------------------------|--------|-----------------------|-----------------------------|-----------------------|-------------|-----------------|

| etching depths                                                | nm     |                       |                             |                       |             |                 |

| waveguide width                                               | nm     | Established           |                             |                       |             |                 |

| resistance<br>measurements                                    | Ω      | Lisuonished           |                             |                       |             |                 |

| on wafer facet coating reflectivity                           | %      | No current capability | No<br>planned<br>capability | Planned<br>Capability | Implemented | Establis<br>hed |

| thickness and refractive<br>index of deposited<br>dielectrica | nm     | Established           |                             |                       |             |                 |

| thickness of overgrowth layers                                | nm     |                       |                             |                       |             |                 |

#### A projection of the key industry needs is shown in Table

Table 10 Key challenges with respect to test between 2020 and 2040

|                                                 | 2020 | 2025 | 2030 | 2035 | 2040 |

|-------------------------------------------------|------|------|------|------|------|

| Adopt semiconductor EIC industry test practices |      |      |      |      |      |

| Test procedures from custom to standardized     |      |      |      |      |      |

| Standardization of test structures              |      |      |      |      |      |

| Test data exchangeability and analysis          |      |      |      |      |      |

| Technology agnostic testing                     |      |      |      |      |      |

| Test automation                                 |      |      |      |      |      |

| Design for test                                 |      |      |      |      |      |

| Application agnostic testing                    |      |      |      |      |      |

*Red:* Not current industry practice; Orange: Partial industrial coordination; Yellow: Significant industrial coordination and compatibility; Green: Established Industry standard.

Each category is broken down in more specific subcategories in the following tables, following the same roadmap guidelines. Each table addresses areas such as key challenges, test practices, transition from custom to standardized procedures, transfer of data, adopting semiconductor test practices, design for test both at the die level and the software level. The tables show competences going out beyond 5 years and emphasize relative strengths for each area.

Table 11: Adopt semiconductor EIC industry test practices

|                                              | 2020 | 2025 | 2030 | 2035 | 2040 |

|----------------------------------------------|------|------|------|------|------|

| 6 Sigma methodology                          |      |      |      |      |      |

| Documenting and reporting                    |      |      |      |      |      |

| The same metrics but methods may vary        |      |      |      |      |      |

| Optimized test at wafer-level                |      |      |      |      |      |

| DC testing in electrical – electrical domain |      |      |      |      |      |

| Revised accept-reject methodology            |      |      |      |      |      |

Table 12 Transition from custom to standardized procedures.

|                                              | 2020 | 2025 | 2030 | 2035 | 2040 |

|----------------------------------------------|------|------|------|------|------|

| Standards instead of custom approaches       |      |      |      |      |      |

| Prioritize tests across full PIC value chain |      |      |      |      |      |

| Testing metrics                              |      |      |      |      |      |

| Relevance of a test                          |      |      |      |      |      |

| Standardized test structures                 |      |      |      |      |      |

Table 13 Transfer of test data across the PIC value chain

|                                                                                          | 2020 | 2025 | 2030 | 2035 | 2040 |

|------------------------------------------------------------------------------------------|------|------|------|------|------|

| Implementation in PDK<br>Improved design tools (EPDA)                                    |      |      |      |      |      |

| Correlation of the test outcomes<br>Improved processes<br>Identification of redundancies |      |      |      |      |      |

| Accessible scope – potential IP issues                                                   |      |      |      |      |      |

Table 14 Technology agnostic testing

|                                                | 2020 | 2025 | 2030 | 2035 | 2040 |

|------------------------------------------------|------|------|------|------|------|

| Across (currently) major technologies          |      |      |      |      |      |

| InP, SiPH SiN, Electro-Optic (EO) polymers     |      |      |      |      |      |

| Open for emerging platforms                    |      |      |      |      |      |

| polymer, diamond, rare earth ion doped, three- |      |      |      |      |      |

| dimensional (3D) PICs, SoC (high temperature)  |      |      |      |      |      |

| Hybrid integration                             |      |      |      |      |      |

| photonic cross platform                        |      |      |      |      |      |

| electronic-photonic chip level (EPICs)         |      |      |      |      |      |

| electronic-photonic PCB-chip                   |      |      |      |      |      |

| Testing PICs with CMOS circuits/testing        |      |      |      |      |      |

Table 15 Automation of test at wafer, bar, die, module and system level testing

|                                              | 2020 | 2025 | 2030 | 2035 | 2040 |

|----------------------------------------------|------|------|------|------|------|

| Wafer - level                                |      |      |      |      |      |

| Bar and die – level testing                  |      |      |      |      |      |

| Standard test interfaces (layout templates)  |      |      |      |      |      |

| Technology agnostic                          |      |      |      |      |      |

| Scalability                                  |      |      |      |      |      |

| On-chip self-diagnostics                     |      |      |      |      |      |

| (Utilizing electrical-to-electrical testing) |      |      |      |      |      |

Table 16 Design for test

|                                      | 2020 | 2025 | 2030 | 2035 | 2040 |

|--------------------------------------|------|------|------|------|------|

| Test oriented layout templates       |      |      |      |      |      |

| Implementation in PDKs               |      |      |      |      |      |

| Test scripts for generic die testing |      |      |      |      |      |

| Training of PIC designers            |      |      |      |      |      |

#### SITUATION ANALYSES

#### MANUFACTURING PROCESSES

#### Design

Testing is a time consuming and complex task, and a significant contribution on the final cost of a device, but essential at different stages in the development of a photonic integrated circuit. Testing aims to verify fab process tolerances, validate foundry manufacturing, extract building block parameters, and analyze system level performance of overall circuits. Since there is a sheer variety of PIC designs, it is very complicated to have a generic or application independent testing procedure.

Testing starts at the design stage. On one hand, foundries design their own test cells for process control monitoring (PCM), containing specific structures to verify and validate the wafer fabrication, ensure basic building block performance, obtain statistics for PDK maturing, and estimate yield. On the other hand, designers should also include *smart* and *proper* test structures in their designs, not only to ease the testing task later on, but to verify complete design functionality, extract additional parameters, and to corroborate data provided by foundries. However, there are currently no standards for these test structures, so it usually depends on the designer's experience and proper communication with testing engineers.

In a view of the PIC production chain as depicted in Figure 3 after the design stage, actual testing can be divided into a number of categories: wafer level, bar level, bare die level and package level.

There are three main drivers to develop integrated photonic solutions, particularly in telecom and datacom applications. The first driver is the cost of integrated photonics modules tracks much closer to the cost of traditional electronic ICs and are a fraction of the cost of the traditional optical solutions. The second driver is that Integrated Photonic modules are also much lower power and smaller. The third driver is that, integrated photonic modules offer much more in terms of scaling towards ever growing demand for bandwidth and speed.

Commercial companies are designing and manufacturing integrated photonics modules for all of the above reasons. Companies must be able to sell these modules, whilst maintaining acceptable profit margins as expected by the financial markets. To obtain these margins, yields need to be high and the cost of test low. This applies to the cost of test equipment for both validation and production.

The end to end cost to manufacture, assembly and test of a complete integrated photonic module must be taken into account, when designing the PIC, the electrical ICs and picking the composite components. Thought needs to be given to how much electrical testing can be done, that will predict the functioning of the optical waveguides, and whether there are optical wafer acceptance test parameters that will also predict functioning devices.

An automated test equipment (ATE) for optical solutions is difficult and expensive to implement and may not well represent the performance of the final integration of a laser and other components into the modules. For example, if the electrical testing of the PIC can be 95% accurate to predict good die, the cost calculation may show that it is actually cheaper to throw away bad modules built with the 5% bad die, than to pay for ATE for optical test. It is recommended that commercial photonic companies do an end to end cost and yield analysis of each test step vs the cost of test equipment to understand the most cost-effective test solutions.

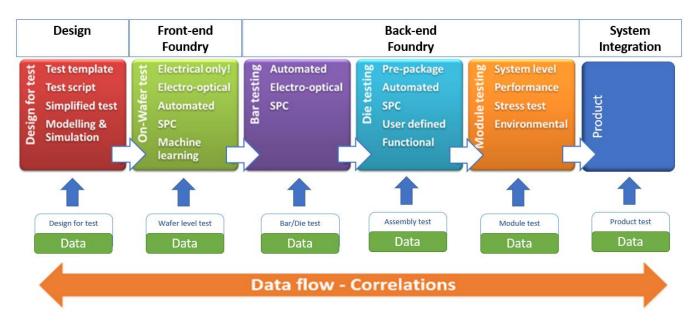

It is very important to keep the data collected across the production chain into account during the design phase and the complete process as depicted in Figure 4. Test results are collected and analyzed by designers and manufacturing engineers at each individual step. Although the nature of test at each step differs a data flow allowing for open exchange between all stages is crucial for development of correlations and optimization of test processes.

Figure 4. Test framework for data flow and exchange across production chain from a design to product (<u>www.openepda.org</u>).

Test frameworks (www.openepda.org) utilizing open standards assure data interoperability, exchangeability and traceability, inherently enable such data flow. Such test framework is hardware agnostic and can be deployed around any tool and equipment configuration. It decouples operators from low-level hardware control, allows for dynamically adjusted test sequences and customized analysis modules. Machine learning techniques may further augment the capabilities of such an approach by increasing efficiency of data analysis and decision making.

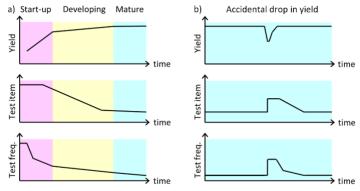

The demand for test differs at different development stages of the manufacturing process as suggested in Figure 5(a). It is particularly important at initial start-up phase and changes as the manufacturing process develops. The rate of this change is different at each phase and is inversely proportional to the yield. The cost of test is proportional to the product of the number of items tested, frequency of test events and the production volume. Also, since the cost of test must be borne by the passing devices, the cost of test per good-device goes up significantly as the yield drops (Figure 5 (b)). The long-term cost of test trend follows the demand for test and gradually decreases as the manufacturing process matures.

Figure 5. (a) Demand for test at different development stages of production process over time in perspective of yield, number of tested items and frequency / number of test cycles of test events. (b) Disruptive event in yield with an impact on number of tested items and test frequency.

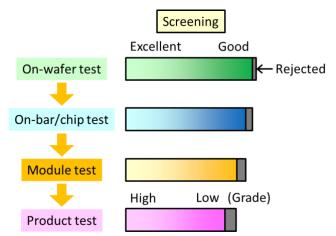

In order to manufacture efficiently, certain level to test for screening has to be considered and put in place at different points of production chain, as presented in the Figure 6.

Figure 6. Test for screening is essential to manufacture products efficiently.

The wide spread of test processes across the full production chain results in massive test data being collected in the manufacturing process. Test strategy for keeping high yield, screening, etc. is determined based on such massive test data and it is very important to establish the best test strategy. This will remain challenging because the best test strategy varies in each situation.

#### Wafer level Testing

Wafer testing is mainly carried out by front-end foundries and test houses, and provide both, visual and electrical and/or optical testing.

Within the foundry, during wafer manufacturing, both visual inspection and quantitative measurements are performed at each step in the fabrication process. The primary goal here is to examine the wafer for irregularities in the process. For example, film thicknesses, etch depths, and line widths can all experience process variations. Most of these measurements are part of the standard suite of inspection methods for electronic ICs. The visual inspection is still manual much of the time and is usually executed only in limited regions of the wafer, requiring machine vision systems providing enough resolution, multi axes positioners and capability to inspect different wafer sizes and materials. Once the fabrication process is complete, and before singulation, final wafer metrology is carried out.

Optical microscopes are useful for obtaining physical dimensions of the fabricated structures, layer thicknesses, surface roughness, and (for III-V materials) can also create photoluminescence maps, giving information of material composition and quality, bandgap determination, etc. Modern digital microscopes have sophisticated stitching and profilometry algorithms that can provide an accurate picture of trench depths, and waveguide path accuracy over relatively large areas.

Scanning electron microscopy (SEM) testing has always been important technique at the wafer level. However, integrated photonics circuits add a level of difficulty to SEM testing because of the insulating oxide layers both above and below the silicon and silicon nitride waveguides. These oxide layers result in charging; without a conductive coating on the wafer surface, an oxide-coated PIC may yield a distorted image.

TEST

Since defects/irregularities detection at this early stage of the development will have a great impact on the final cost of PIC development, it would be necessary to develop test pattern-recognition algorithms for the visual inspection and metrology and formulate a pass or fail criteria depending on technology (InP, SiN, SiPh, etc) and structures.

At the wafer level, along with visual inspection and taking advantage of the pre-existing equipment for CMOS technology, electrical testing can also be carried out. As a matter of fact, at this level, electrical measurements are easier than optical ones, due to the fact that, at the wafer level, coupling light to, or extracting light from individual dies is a challenging task given the tight tolerances required. Electrical measurements can be carried out much faster and at lower equipment cost.

The straightforward approach to carry out optical tests is by means of vertical grating couplers. However, these structures can only be implemented in a few technologies (e.g. SiPh, SiN) and have limited spectral bandwidth. Thus, different structures/approaches have been proposed to overcome these limitations, such as: reflective 45° mirrors, evanescent coupling, etc., or by means of indirect electrical measurements (Contactless Integrated Photonic Probe, CLIPP)<sup>2</sup> when possible.

Even though, optical testing is still challenging. Wafer prober stations are difficult to interface with optical probes, so both need to be adapted/designed accordingly to the requirements, and this makes the resulting solutions not very flexible, increasing the throughput but limiting the re-usability for different applications.

Furthermore, optical probes require (semi-)automated alignment, with very high resolution.

#### Bare die level Testing

Ideally, foundries should provide both parameter values and their expected statistical variation to end-users; these are usually built into the parametric models used to describe each building block in the photonics process design kits. However, due to all of the challenges associated with optical testing at wafer level, bare die testing is still carried out to extract most building block parameters.

Bare die testing typically has low levels of automation and is therefore costly and complex. Thus, only a small subset of tests and structures are measured by the foundry, and it is up to test houses or end-users to carried out more complex, extensive characterization of individual building blocks, or system level functionalities of the overall circuit.

It is worth noting that many measurement procedures for PIC testing are not yet standardized. This is true both for testing of individual building blocks (sub circuits and devices) as well as for full, functional circuits. This often leads to a wide variety of test setups (leading to different measurement results) between foundries, test houses, designers, and end-users. Defining standards/procedures at this early stage of the technology may seem too ambitious, but instead what is proposed in the short term, is to define good practices.

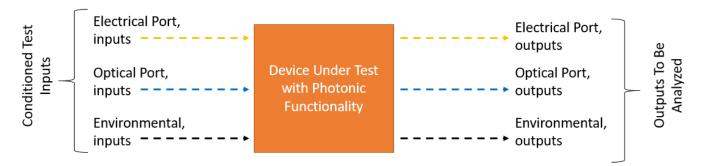

#### Generic Photonic Device Testing

Figure 7 illustrates the general test requirement; the need for both electrical and optical test inputs, and then analysis of the electrical and optical outputs from the device under test (DUT). In addition, environmental parameters, such as temperature, humidity, vibration, etc. may be test inputs. Finally, in addition to the optical and electrical test responses, physical factors, such as temperature rise, may be outputs that are monitored during testing.

<sup>&</sup>lt;sup>2</sup> F. Morichetti et al., "Non-Invasive On-Chip Light Observation by Contactless Waveguide Conductivity Monitoring," in IEEE Journal of Selected Topics in Quantum Electronics, vol. 20, no. 4, pp. 292-301, July-Aug. 2014. doi: 10.1109/JSTQE.2014.2300046

#### Figure 7 Generic Photonic Product Test Environment

The electrical ports are electrical contacts, or arrays of contacts, for power, control, monitoring of functionality, and, of course, data inputs and/or outputs.

The light directed to an optical input port may be in the form of one or more optical beams or it can be guided by one or more fibers. In either case, it is typical to arrange the parallel inputs in a regular array, the size of which must be considered in the PIC design. The light can either be a constant source (that is then modulated by the device under test) or it can carry a modulated data stream (if the intended function of the device is to de-modulate the data). The optical interconnections may be in the form of butt/edge coupling, a grating coupler, or an evanescent coupling resulting from proximity of parallel waveguides. Making these test connections, especially the optical connections, is frequently a major project.

The photonic input and output signals may have multiple parameters needing measurement. Specifically, optical signals may require measurement of the following properties of individual sources, lanes or channels:

- Power

- Polarization

- Direction

- Mode profile

- Wavelength

- Variation in any parameter (e.g. power, wavelength, polarization) over time

- o modulation (fast)

- o drift (slow)

- Skew between beams

- Component loss

- Return loss

System (functional) properties:

- Signal-to-Noise Ratio (SNR), Relative Intensity Noise (RIN), Phase-Noise, Crosstalk

- Bit error rate (BER)

- Variation of system figures of merit with temperature and other environmental inputs

A typical measurement requires a source with a means of controlling one or more of these parameters. The source will typically be coupled into a single mode fiber that, for some systems, must be polarization maintaining. The source can be tunable (in cases where the wavelength dependence is part of the measurement), narrowband (for monochromatic measurements) or broadband in certain sensors applications. The light is injected into waveguides via optical ports and routed (according to the PIC design) through one or more active or passive components. Active components typically require one or more electronic drive signals. These components (the devices under test) will modify the input optical signals in a manner determined by the magnitude, phase, and frequency of the electrical drive signals. The resulting electrical and optical signals are on the corresponding output ports.

Environmental inputs may include all of the usual variables: temperature, humidity, temperature cycling, Highly Accelerated Stress Test (HAST), vibration, shock, etc.

Physical outputs include temperature rise, mechanical changes such as delamination, cracking, swelling, wire breaks or optical chain interruptions, etc.

Photonic test requirements vary by the test level (wafer, die, photonic SiP, system) and test need (access, sources, detectors, functions). Table 17, Photonic Test Requirements gives a generic view of the testing needs for items containing photonic elements at the various levels.

A similar table can be developed for specific applications to provide some insight into the related requirements for each application.

|                          |                                                                                                                                                                               |                                                                                                  | Test Need                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                     |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Level               | <b>Optical Access</b>                                                                                                                                                         | Sources                                                                                          | Detectors                                                                                                                                                                                   | Functions                                                                                                                                                                                                                                                                                           |

| Wafer                    | 45° mirrors,<br>vertical grating<br>couplers, etched<br>factes, cleaved<br>fiber, tapered<br>fiber, lensed<br>fiber, focused<br>free-space<br>beam,<br>evanescent<br>coupling | External<br>sources<br>injected via<br>fiber or free-<br>space access<br>Integrated<br>sources   | External<br>photodetectors,<br>potentially in arrays;<br>Imaging sensors<br>Optics to collect<br>and/or image light to<br>be detected.<br>Integrated<br>photodetectors                      | Wide variety of device<br>characterization and functional<br>tests; media loss/cm, insertion<br>loss, modulation<br>depth/bandwidth, polarization<br>control, wafer uniformity,<br>detector sensitivity/responsivity,<br>temperature sensitivity, die-to-<br>die variation, skew between<br>outputs |

| Chip                     | The same as<br>wafer options<br>plus edge<br>coupling to<br>embedded or<br>surface<br>waveguides.                                                                             | The same as<br>wafer options                                                                     | The same as wafer options                                                                                                                                                                   | The same as wafer options plus<br>edge coupling impacts on loss,<br>spectral bandwidth and<br>polarization                                                                                                                                                                                          |

| Photonic SiP             | Butt coupling or<br>expanded beam<br>connector,<br>evanescent<br>coupling, fiber<br>splice, ribbon<br>fiber splice                                                            | External or<br>on-chip laser<br>source to<br>simulate<br>application<br>related<br>requirements. | External detector or<br>detectors, potentially<br>in an array, gathering<br>light from an edge<br>emitting waveguide<br>or vertical emitting<br>45° mirror, or vertical<br>emitting grating | The same as wafer and chip<br>options, plus characterize<br>package connections, and<br>application specific tests such as<br>eye diagrams, BER,<br>environmental sensitivity                                                                                                                       |

| System                   | Conventional<br>optical<br>connector, fiber<br>splice                                                                                                                         | External or<br>internal laser<br>source or<br>sources to<br>simulate<br>inputs.                  | As needed to measure<br>and evaluate system<br>outputs.                                                                                                                                     | Intensity, skew between lanes,<br>polarization, eye diagram, SNR,                                                                                                                                                                                                                                   |

| In Use, Over<br>Lifetime | Limited, if any.<br>System<br>dependent<br>access.                                                                                                                            | Both self and<br>remotely<br>initiated data<br>reporting                                         | Primarily wireless or electronic                                                                                                                                                            | Monitor & report performance changes. Initiate self-repair.                                                                                                                                                                                                                                         |

Table 17: Photonic Test Requirements

Several types of product testing of devices, including those with photonic capability, usually are required:

- Test during development to ensure the design "works"

- Qualification testing, typically done before a product is committed to wide use

- In-process testing to monitor manufacturing process quality

- Final testing before each individual product is shipped to a customer

#### GENERAL TEST EQUIPMENT

Optical device test equipment is available from multiple suppliers. Historically, the telecommunications industry was the major consumer, but in recent years the use of optical communications for short distances, such as Local Area Networks (LANS), Fiber to the X (Home, Office, Curb, Node, etc.) (FTTX), and Active Optical Cable (AOC) and in Data Centers, as well as a variety of sensors, has broadened the demand. Much of the demand emerging for these new optical applications is filled by utilizing equipment developed for and derived from that used by the Telecom sector. As these applications grow in importance, specialized equipment is emerging and becoming available.

Devices under test can vary dramatically, so defining all the needed instruments for PIC testing is not the most appropriate approach. Since electrical and optical domains merge in PICs, optical and electrical equipment is needed. In the long run, testing should be as automated as possible, meaning that wafer level testing should provide known good dies, reducing the fraction of dies that need to be tested at the package level. However, standard wafer probe stations are mainly intended for electrical testing, so the main challenge is to customize the probe station so that it is equipped to carry out complete (optical and electrical) testing. After dicing, a pick-up element with accompanying alignment metrology is necessary to release and properly place dies for testing on a thermally controlled stage.

#### CRITICAL (INFRASTRUCTURE) ISSUES

In general, the ambition in manufacturing is to measure as little as is necessary to gain the relevant information on product quality. However, to reduce the **assembly related** costs it is essential to closely monitor the complete fabrication process of the photonic integrated circuits (PIC) or even of the final device. While this may appear to be a very expensive procedure, test and selection after fabrication and assembly is even more expensive. A critical point here is to select the good dies at a very early stage (i.e. the wafer stage) in the manufacturing chain. This is referred to be as known-good-dies.

Beginning with wafer level production, each cleanroom step needs to be measured and validated. Since the silicon photonics manufacturing utilizes CMOS processes, it can benefit from such well-established characterization methods as ellipsometry, atomic-force microscopy (AFM), scanning-electron microscopy (SEM), white light surface profilometry and optical microscopy for layer thickness, critical dimension (CD) and line edge roughness measurements. These methods are well known and well established throughout the industry and, when used appropriately, can guarantee high throughput and high yield. For photonic integration technologies on other substrates and using other material systems compatibility with CMOS optimized tooling is limited, hence transfer of those test and characterization methods may require additional R&D efforts for adoption to such technology processes. In addition, the electrical tests of the integrated circuits are quite well established. Automated test equipment, test heads including specially adapted probe cards of different designs in combination with fully automated wafer probers contribute as well to a high throughput for the electrical measurements in manufacturing chain of integrated circuits (ICs). An exception to this is the need for electronic probes for very high bandwidth detectors, since it is not yet standard practice to automatically test electronic circuits at speeds higher than 40 GHz.

The equipment infrastructure for photonic measurements is not as mature as that for electrical test equipment. One major challenge for the coming years will be to assure availability of high volume and high throughput die & wafer level (WL) measurement equipment for photonic integrated circuits and electronic-photonic integrated circuits, so called EPICs. A logical step would be to extend the electronic test equipment to enable photonic measurements using a similar physical architecture. For wafer level measurements, this would correspond to optical solutions within the:

- Wafer prober / wafer handler

- Probe Card

- Automated Test Equipment (Test head or test matrix, measurement instruments)

The wafer prober and wafer handler need to be similar in structure. They handle the wafers, do the x,y,z and theta alignment and step through the devices on the wafer. A feedback from the automated test equipment is beneficial but all current probers are capable of handling such input. However, the prober needs to be optimized for the particular optical input/output ports to be probed. For example, an edge input/output requires an optical fiber probe with a turning mirror, and must be aligned both in angle and position (typically better than 1  $\mu$ m) to accomplish the coupling. A grating coupler has more relaxed positional tolerance but requires precise angular control. In both cases, the mechanical requirements are more stringent than is required to probe electronic test pads. For very high speed applications, the electrical bandwidth of the probe card may need to exceed 40 GHz. When probing detectors directly, it is then helpful to include a transimpedance amplifier in the probe head.

There are currently several suppliers of automated test equipment who provide tools such as high-speed optical power meters or optical network analyzers that allow engineers to develop a measurement setup very similar to the IC test setups.

The real challenge is to feed and read out the optical and electrical signals together to and from the device under test. In case of pure electrical probe cards, the electrical contact needles (e.g. cantilever, vertical or MEMS needles) provide physical contact to the DUT bond pads. In case of standard IC probers, the alignment tolerances of several micrometers between electrical interface (needles) and device under test are quite moderate.

The optical interface will be realized by a grating coupler on the DUT side and a waveguide of some kind, e.g. an optical fiber, on the prober side. The lateral tolerances for such an optical interface are much tighter and lie in the sub-micrometer range. This gap between the two tolerance ranges will make it difficult to extent the electronic measurement equipment to the photonic measurements or even ensure a compatibility of common IC-Wafer level test equipment and procedures.

It is critical to correlate the physical measurements to both the specific functional measurements and the overall behavior of the photonic integrated circuit.

Some physical measurements (for example, loss measurements, spectral bandwidth, polarization dependence) are very straightforward. Others present a more significant challenge; for example, a suitable measurement of the effective index and group index of the waveguide mode and accurate measurements of the modal profile near couplers are critical measurements that are not yet standardized.

In future, calibration facilities will be needed to provide calibration targets which can be traced back to a standard. For instance, test PICs calibrated for known component loss, waveguide loss, and dispersion could be made available to equipment manufacturers, foundries and packaging facilities. This is especially important when new materials are introduced; in such cases both the performance from a materials standpoint, as well as a device performance standpoint will be vital. Calibration facilities could be e.g. NIST (USA), PTB (Germany) or NPL (Great Britain).

#### **TECHNOLOGY NEEDS (RELATED TO MILESTONES)**

This chapter focusses on the technological needs regarding testing tools, methods, measurement time, capacity, speed, and accuracy. For an efficient workflow between the different production partners (e.g. design houses, wafer processing fab, backend and packaging groups and customer) standardized measurement techniques with defined measurement data transfer are a stringent requirement. These topics will be addressed in the following sections.

#### **PRIORITIZED RESEARCH NEEDS**

Prioritized research needs that require results in less than five years include the following: Ability to test photonic properties of wafers during fab to ensure that wafers are good.

Processing ever-faster (100Gbps+) data streams. Test time is often determined and limited by memory I/O data rates so increasing these will remove a barrier to lower cost. Developing test equipment with more capability than the devices to be tested is a continually moving target!